ની ડિઝાઇનફોટોનિકસંકલિત સર્કિટ

ફોટોનિક ઇન્ટિગ્રેટેડ સર્કિટ્સ(PIC) ઘણીવાર ગાણિતિક સ્ક્રિપ્ટોની મદદથી ડિઝાઇન કરવામાં આવે છે કારણ કે ઇન્ટરફેરોમીટર અથવા પાથ લંબાઈ પ્રત્યે સંવેદનશીલ અન્ય એપ્લિકેશનોમાં પાથ લંબાઈનું મહત્વ ખૂબ જ વધારે છે.ચિત્રતે વેફર પર બહુવિધ સ્તરો (સામાન્ય રીતે 10 થી 30) ને પેટર કરીને બનાવવામાં આવે છે, જે ઘણા બહુકોણીય આકારોથી બનેલા હોય છે, જે ઘણીવાર GDSII ફોર્મેટમાં રજૂ થાય છે. ફોટોમાસ્ક ઉત્પાદકને ફાઇલ મોકલતા પહેલા, ડિઝાઇનની શુદ્ધતા ચકાસવા માટે PIC નું અનુકરણ કરવામાં સક્ષમ હોવું ખૂબ ઇચ્છનીય છે. સિમ્યુલેશનને બહુવિધ સ્તરોમાં વિભાજિત કરવામાં આવે છે: સૌથી નીચું સ્તર ત્રિ-પરિમાણીય ઇલેક્ટ્રોમેગ્નેટિક (EM) સિમ્યુલેશન છે, જ્યાં સિમ્યુલેશન સબ-તરંગલંબાઇ સ્તરે કરવામાં આવે છે, જોકે સામગ્રીમાં અણુઓ વચ્ચેની ક્રિયાપ્રતિક્રિયાઓ મેક્રોસ્કોપિક સ્કેલ પર નિયંત્રિત થાય છે. લાક્ષણિક પદ્ધતિઓમાં ત્રિ-પરિમાણીય મર્યાદિત-તફાવત સમય-ડોમેન (3D FDTD) અને ઇજેનમોડ વિસ્તરણ (EME) શામેલ છે. આ પદ્ધતિઓ સૌથી સચોટ છે, પરંતુ સમગ્ર PIC સિમ્યુલેશન સમય માટે અવ્યવહારુ છે. આગળનું સ્તર 2.5-પરિમાણીય EM સિમ્યુલેશન છે, જેમ કે મર્યાદિત-તફાવત બીમ પ્રચાર (FD-BPM). આ પદ્ધતિઓ ખૂબ ઝડપી છે, પરંતુ થોડી ચોકસાઈનો ભોગ આપે છે અને ફક્ત પેરાક્સિયલ પ્રચારને હેન્ડલ કરી શકે છે અને ઉદાહરણ તરીકે, રેઝોનેટર્સનું અનુકરણ કરવા માટે તેનો ઉપયોગ કરી શકાતો નથી. આગળનું સ્તર 2D EM સિમ્યુલેશન છે, જેમ કે 2D FDTD અને 2D BPM. આ પણ ઝડપી છે, પરંતુ મર્યાદિત કાર્યક્ષમતા ધરાવે છે, જેમ કે તેઓ ધ્રુવીકરણ રોટેટર્સનું અનુકરણ કરી શકતા નથી. આગળનું સ્તર ટ્રાન્સમિશન અને/અથવા સ્કેટરિંગ મેટ્રિક્સ સિમ્યુલેશન છે. દરેક મુખ્ય ઘટક ઇનપુટ અને આઉટપુટ સાથેના ઘટકમાં ઘટાડી દેવામાં આવે છે, અને કનેક્ટેડ વેવગાઇડ ફેઝ શિફ્ટ અને એટેન્યુએશન એલિમેન્ટમાં ઘટાડી દેવામાં આવે છે. આ સિમ્યુલેશન અત્યંત ઝડપી છે. આઉટપુટ સિગ્નલ ટ્રાન્સમિશન મેટ્રિક્સને ઇનપુટ સિગ્નલ દ્વારા ગુણાકાર કરીને મેળવવામાં આવે છે. સ્કેટરિંગ મેટ્રિક્સ (જેના તત્વોને S-પેરામીટર્સ કહેવામાં આવે છે) ઘટકની બીજી બાજુ ઇનપુટ અને આઉટપુટ સિગ્નલો શોધવા માટે એક બાજુ ઇનપુટ અને આઉટપુટ સિગ્નલોનો ગુણાકાર કરે છે. મૂળભૂત રીતે, સ્કેટરિંગ મેટ્રિક્સમાં તત્વની અંદર પ્રતિબિંબ હોય છે. સ્કેટરિંગ મેટ્રિક્સ સામાન્ય રીતે દરેક પરિમાણમાં ટ્રાન્સમિશન મેટ્રિક્સ કરતા બમણું મોટું હોય છે. સારાંશમાં, 3D EM થી ટ્રાન્સમિશન/સ્કેટરિંગ મેટ્રિક્સ સિમ્યુલેશન સુધી, સિમ્યુલેશનનો દરેક સ્તર ઝડપ અને ચોકસાઈ વચ્ચે ટ્રેડ-ઓફ રજૂ કરે છે, અને ડિઝાઇનર્સ ડિઝાઇન માન્યતા પ્રક્રિયાને ઑપ્ટિમાઇઝ કરવા માટે તેમની ચોક્કસ જરૂરિયાતો માટે સિમ્યુલેશનનું યોગ્ય સ્તર પસંદ કરે છે.

જોકે, ચોક્કસ તત્વોના ઇલેક્ટ્રોમેગ્નેટિક સિમ્યુલેશન પર આધાર રાખવો અને સમગ્ર PIC નું અનુકરણ કરવા માટે સ્કેટરિંગ/ટ્રાન્સફર મેટ્રિક્સનો ઉપયોગ કરવાથી ફ્લો પ્લેટની સામે સંપૂર્ણપણે સાચી ડિઝાઇનની ગેરંટી મળતી નથી. ઉદાહરણ તરીકે, ખોટી ગણતરી કરેલ પાથ લંબાઈ, મલ્ટિમોડ વેવગાઇડ્સ જે હાઇ-ઓર્ડર મોડ્સને અસરકારક રીતે દબાવવામાં નિષ્ફળ જાય છે, અથવા બે વેવગાઇડ્સ જે એકબીજાની ખૂબ નજીક હોય છે જે અણધારી જોડાણ સમસ્યાઓ તરફ દોરી જાય છે તે સિમ્યુલેશન દરમિયાન શોધી શકાતા નથી. તેથી, જો કે અદ્યતન સિમ્યુલેશન ટૂલ્સ શક્તિશાળી ડિઝાઇન માન્યતા ક્ષમતાઓ પ્રદાન કરે છે, તેમ છતાં ડિઝાઇનની ચોકસાઈ અને વિશ્વસનીયતા સુનિશ્ચિત કરવા અને ફ્લો શીટના જોખમને ઘટાડવા માટે, ડિઝાઇનર દ્વારા વ્યવહારુ અનુભવ અને તકનીકી જ્ઞાન સાથે ઉચ્ચ સ્તરની તકેદારી અને કાળજીપૂર્વક નિરીક્ષણની જરૂર છે.

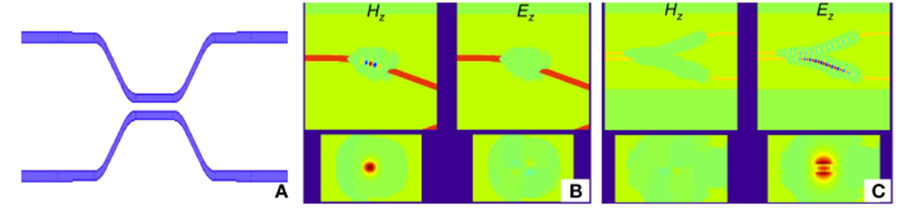

સ્પાર્સ FDTD નામની ટેકનિક ડિઝાઇનને માન્ય કરવા માટે સંપૂર્ણ PIC ડિઝાઇન પર સીધા 3D અને 2D FDTD સિમ્યુલેશન કરવાની મંજૂરી આપે છે. કોઈપણ ઇલેક્ટ્રોમેગ્નેટિક સિમ્યુલેશન ટૂલ માટે ખૂબ મોટા પાયે PICનું અનુકરણ કરવું મુશ્કેલ હોવા છતાં, સ્પાર્સ FDTD એકદમ મોટા સ્થાનિક વિસ્તારનું અનુકરણ કરવામાં સક્ષમ છે. પરંપરાગત 3D FDTD માં, ચોક્કસ ક્વોન્ટાઇઝ્ડ વોલ્યુમમાં ઇલેક્ટ્રોમેગ્નેટિક ક્ષેત્રના છ ઘટકોને પ્રારંભ કરીને સિમ્યુલેશન શરૂ થાય છે. જેમ જેમ સમય આગળ વધે છે, વોલ્યુમમાં નવા ક્ષેત્ર ઘટકની ગણતરી કરવામાં આવે છે, અને તેથી વધુ. દરેક પગલા માટે ઘણી ગણતરીની જરૂર પડે છે, તેથી તે ઘણો સમય લે છે. સ્પાર્સ 3D FDTD માં, વોલ્યુમના દરેક બિંદુ પર દરેક પગલા પર ગણતરી કરવાને બદલે, ક્ષેત્ર ઘટકોની સૂચિ જાળવવામાં આવે છે જે સૈદ્ધાંતિક રીતે મનસ્વી રીતે મોટા વોલ્યુમને અનુરૂપ હોઈ શકે છે અને ફક્ત તે ઘટકો માટે જ ગણતરી કરી શકાય છે. દરેક સમય પગલા પર, ક્ષેત્ર ઘટકોને અડીને આવેલા બિંદુઓ ઉમેરવામાં આવે છે, જ્યારે ચોક્કસ પાવર થ્રેશોલ્ડથી નીચેના ક્ષેત્ર ઘટકો છોડી દેવામાં આવે છે. કેટલીક રચનાઓ માટે, આ ગણતરી પરંપરાગત 3D FDTD કરતા ઘણી વધુ ઝડપી હોઈ શકે છે. જોકે, વિખેરાઈ રહેલા માળખા સાથે કામ કરતી વખતે સ્પાર્સ FDTDS સારું પ્રદર્શન કરતું નથી કારણ કે આ સમય ક્ષેત્ર ખૂબ ફેલાય છે, પરિણામે એવી યાદીઓ બને છે જે ખૂબ લાંબી અને મેનેજ કરવી મુશ્કેલ હોય છે. આકૃતિ 1 પોલરાઇઝેશન બીમ સ્પ્લિટર (PBS) જેવા 3D FDTD સિમ્યુલેશનનો ઉદાહરણ સ્ક્રીનશોટ બતાવે છે.

આકૃતિ 1: 3D સ્પાર્સ FDTD માંથી સિમ્યુલેશન પરિણામો. (A) એ સિમ્યુલેટેડ સ્ટ્રક્ચરનો ટોચનો દૃશ્ય છે, જે એક દિશાત્મક કપ્લર છે. (B) ક્વાસી-TE ઉત્તેજનાનો ઉપયોગ કરીને સિમ્યુલેશનનો સ્ક્રીનશોટ બતાવે છે. ઉપરોક્ત બે આકૃતિઓ ક્વાસી-TE અને ક્વાસી-TM સિગ્નલોનો ટોચનો દૃશ્ય દર્શાવે છે, અને નીચેના બે આકૃતિઓ અનુરૂપ ક્રોસ-સેક્શનલ દૃશ્ય દર્શાવે છે. (C) ક્વાસી-TM ઉત્તેજનાનો ઉપયોગ કરીને સિમ્યુલેશનનો સ્ક્રીનશોટ બતાવે છે.

પોસ્ટ સમય: જુલાઈ-૨૩-૨૦૨૪